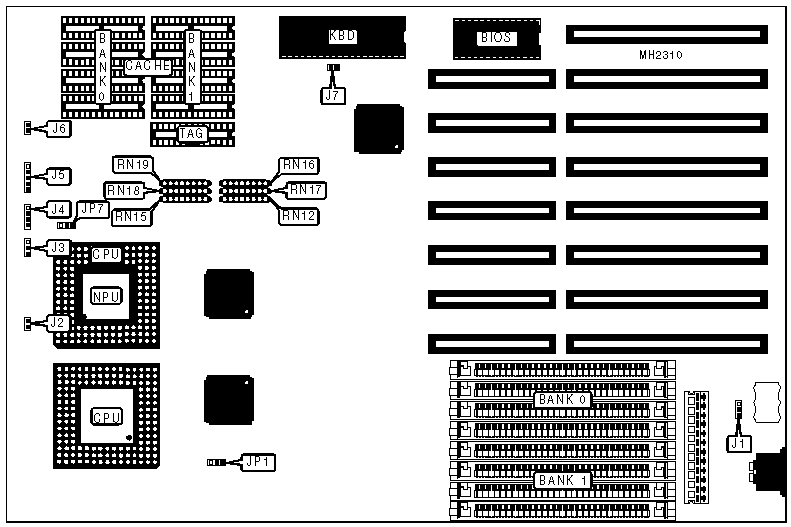

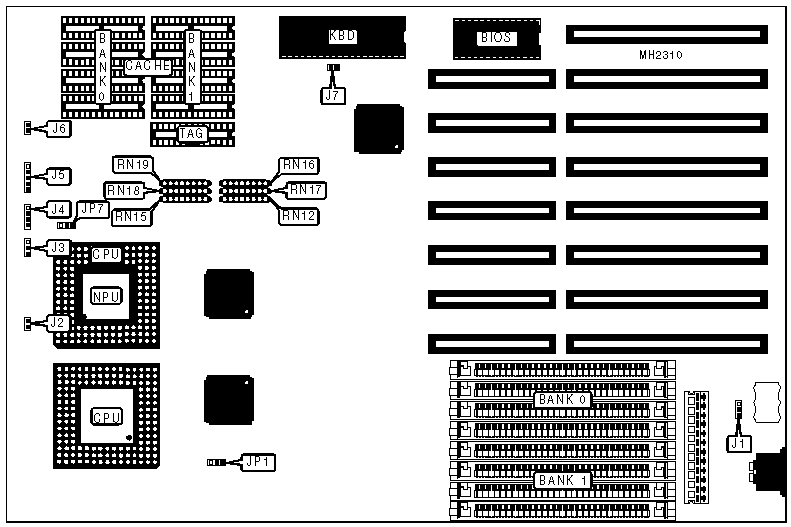

CHAINTECH COMPUTER COMPANY, LTD.

420SXB/425SXB/433SCB/450SCB

|

Processor |

80486SX/80487SX/80486DX/ODP486SX/80486DX2 |

|

Processor Speed |

16/20/25/33/50(internal)/50/66(internal)MHz |

|

Chip Set |

SIS |

|

Max. Onboard DRAM |

32MB |

|

Cache |

64/128/256KB |

|

BIOS |

AMI |

|

Dimensions |

330mm x 218mm |

|

I/O Options |

None |

|

NPU Options |

4167 |

|

CONNECTIONS | |||

|

Purpose |

Location |

Purpose |

Location |

|

External battery |

J1 |

Speaker |

J4 |

|

Turbo LED |

J2 |

Power LED & keylock |

J5 |

|

Turbo switch |

J3 |

Reset switch |

J6 |

|

USER CONFIGURABLE SETTINGS | |||

|

Function |

Jumper |

Position | |

|

» |

Turbo enabled |

J3 |

Closed |

|

Turbo disabled |

J3 |

Open | |

|

» |

Monitor type select monochrome |

J7 |

Open |

|

Monitor type select color |

J7 |

Closed | |

|

DRAM CONFIGURATION | ||

|

Size |

Bank 0 |

Bank 1 |

|

1MB |

(4) 256K x 9 |

NONE |

|

2MB |

(4) 256K x 9 |

(4) 256K x 9 |

|

4MB |

(4) 1M x 9 |

NONE |

|

8MB |

(4) 1M x 9 |

(4) 1M x 9 |

|

16MB |

(4) 4M x 9 |

NONE |

|

20MB |

(4) 1M x 9 |

(4) 4M x 9 |

|

32MB |

(4) 4M x 9 |

(4) 4M x 9 |

|

CACHE CONFIGURATION | |||

|

Size |

Bank 0 |

Bank 1 |

TAG |

|

64KB |

(4) 8K x 8 |

(4) 8K x 8 |

(1) 8K x 8 |

|

128KB |

(4) 32K x 8 |

NONE |

(1) 8K x 8 |

|

256KB |

(4) 32K x 8 |

(4) 32K x 8 |

(1) 32K x 8 |

|

CACHE JUMPER CONFIGURATION | ||||||

|

Size |

RN12 |

RN15 |

RN16 |

RN17 |

RN18 |

RN19 |

|

64KB |

Installed |

Installed |

Not installed |

Not installed |

Not installed |

Not installed |

|

128KB |

Not installed |

Not installed |

Not installed |

Installed |

Installed |

Not installed |

|

256KB |

Not installed |

Not installed |

Installed |

Not installed |

Not installed |

Installed |

|

CPU TYPE CONFIGURATION | |

|

Type |

JP7 |

|

80486SX |

pins 2 & 3 closed |

|

ODP486SX |

pins 2 & 3 closed |

|

80487SX |

pins 2 & 3 closed |

|

80486DX |

pins 1 & 2 closed |

|

80486DX2 |

pins 1 & 2 closed |

|

CPU SPEED CONFIGURATION | |

|

Speed |

JP1 |

|

16MHz |

pins 2 & 3 closed |

|

20MHz |

pins 2 & 3 closed |

|

> 25MHz |

pins 1 & 2 closed |

|

MISCELLANEOUS TECHNICAL NOTE |

|

Note:If a Weitek coprocessor is desired, the optional daughter board must be installed in CPU socket. |